Can you get the binary data from PLL pins 15 and 16 for ch39? I am just curious if they are correct or if someone flipped a bit. If someone did invert pin 16, some channels would go up and some would go down by 10kHz. For ch 39, pin 16 should be low and pin 15 should be high.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

-

You can now help support WorldwideDX when you shop on Amazon at no additional cost to you! Simply follow this Shop on Amazon link first and a portion of any purchase is sent to WorldwideDX to help with site costs.

Cobra 142 GTL

- Thread starter johne2hotty

- Start date

I'll check that this morning. Thanks and 73sCan you get the binary data from PLL pins 15 and 16 for ch39? I am just curious if they are correct or if someone flipped a bit. If someone did invert pin 16, some channels would go up and some would go down by 10kHz. For ch 39, pin 16 should be low and pin 15 should be high.

They are both high. I see this condition on channel 40. Ch 39 gives the correct combination for 38 I've tried everything to get L13 to tune into the correct channel pattern but its always 10k down. No disturbances were done in and around the 8719 and I get 8 solid volts on the 8719. Nothing different than when the mod was in place, they moved the crystal from its spot along with the tuning cap, added any upper and lower crystal to the noise blanker/limiter switch and cut some traces to free up the switch for the mod. I pulled all that out and placed the correct crystal and tuning cap back in their respective spots. The clarifier is very odd. Seems like once it gets below the 9 o'clock position everything cuts out. No tx no rx. I took it off the mod and replaced everything as per the sams diagram for the clarifier. Also put back r187 and d36. USB doesnt tune at all to the "5" on TX. Example, 27.385 is 27.388, What the heck am I missing?Can you get the binary data from PLL pins 15 and 16 for ch39? I am just curious if they are correct or if someone flipped a bit. If someone did invert pin 16, some channels would go up and some would go down by 10kHz. For ch 39, pin 16 should be low and pin 15 should be high.

I dont think its your case, but I had a PC68XL that was 5 KHz higher than the read channel. Turned out to be the crystal replacements I bought were the culprit. Grabbed one from a spare parts radio and it worked fine once again. I did fix a 142 GTL a couple years back where LSB worked, and USB didnt. (Or vice versa.) Swapped the crystals to test, and the problem did carry over to the other mode. But what it turned out to be was the diode next to it. Upon scraping off the glue, the diode easily broke off from the corrosion that was happening. Once replacing the diode, both modes were happy.

I have an ARF 2001 that was 10k down in all modes. 12 MHz crystal was off. Ordered a new one from a pinball machine parts site.

Different radio, different situation, same symptom. Drove me nuts trying to figure that one out.

So keep at it. You'll get it. Just may take a while.

Different radio, different situation, same symptom. Drove me nuts trying to figure that one out.

So keep at it. You'll get it. Just may take a while.

The truth table checks out on all channels. The freqs are all up by 10k. Not down by 10k. I tested it for receive using my walkie as the transmitter. I pick up channel 1 by transmitting channel 2. So transmitting my walkie on 38, comes up on 39 on the 142. When I hit the channel skips like 3a andc7a etc, it cross channels so I can barely hear it through the skips. That tells me that the 8719 chip is doing its job. Its probably a disc cap somewhere in the vco because its common in all 3 modes.Can you get the binary data from PLL pins 15 and 16 for ch39? I am just curious if they are correct or if someone flipped a bit. If someone did invert pin 16, some channels would go up and some would go down by 10kHz. For ch 39, pin 16 should be low and pin 15 should be high.

They are all shifted by 10k.im thinking its the VCO area. Mind you, this was someone's hack job. Its a real mess. If I had some base figures to look for it would make it a bit easier. I mean, the sams shows thevtruth tables and voltages all over but no frequency points to look for. With all the multiplying, adding and subtracting thats done they could have at least showed points what to look for.maybe all three modes were shifted at the LO. Check all oscillators and see whats off.

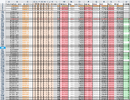

If it has the 11.11125MHz crystal (in AM, it's 11.1116666MHz):If I had some base figures to look for it would make it a bit easier. I mean, the sams shows thevtruth tables and voltages all over but no frequency points to look for. With all the multiplying, adding and subtracting thats done they could have at least showed points what to look for.

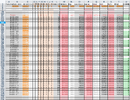

If it has the 11.325MHz crystal:

Thats amazing. Im gonna print these out and study them. Thanks Brandon!If it has the 11.11125MHz crystal (in AM, it's 11.1116666MHz):

View attachment 75539

If it has the 11.325MHz crystal:

View attachment 75540

Such great info. Is this stuff available for all CB radios? Or did you do this in excel?If it has the 11.11125MHz crystal (in AM, it's 11.1116666MHz):

View attachment 75539

If it has the 11.325MHz crystal:

View attachment 75540

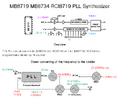

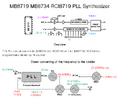

Looks more complicated than it really is. The top two lines have some stuff in them but the rest is just ctrl+D to fill down. Here is a quick rundown on how all the frequencies are mixed.

The 10.24MHz goes into the PLL and is divided by 1024 to create 10kHz (this is the channel step, how much it changes incrementing N). The other side of the phase detector wants to see the same 10kHz, so it will steer the VCO up and down until it sees 10kHz.

To get that other 10kHz, the input needs to see something the divider can get down to 10kHz. The divider can only divide by so much, it has a limited divider range), so the frequency needs to be pretty low going in, around 1MHz. To get this 1MHz signal, the VCO is designed so that when it is mixed with the 11MHz tripler output (33MHz), the output is in the 1MHz range the PLL divider needs to see.

The channel selector gives us a binary N value of 101 for ch19, so 10kHz*101=1.01MHz (this is what must come out of the loop mixer). The tripler is set by the crystal and is fixed at 33.975MHz, so to get 1.01MHz, the VCO needs to make 34.985MHz. and the phase detector will steer it until it reaches it.

The VCO output goes two ways, to the mixer to generate 1MHz as mentioned above, and to the transmit mixer where it is converted to the output frequency.

The logic table provides the N values, and multiplying them by the channel step (10kHz at the phase detector) you get the loop mixer output frequency. Add that to the tripler frequency and you get the VCO frequency. Add that to the mode selection oscillator frequency (the 7.8MHz one) and you get the final frequency.

Thats all the top row of that spreadsheet does, the rest is just filled down.

The 10.24MHz goes into the PLL and is divided by 1024 to create 10kHz (this is the channel step, how much it changes incrementing N). The other side of the phase detector wants to see the same 10kHz, so it will steer the VCO up and down until it sees 10kHz.

To get that other 10kHz, the input needs to see something the divider can get down to 10kHz. The divider can only divide by so much, it has a limited divider range), so the frequency needs to be pretty low going in, around 1MHz. To get this 1MHz signal, the VCO is designed so that when it is mixed with the 11MHz tripler output (33MHz), the output is in the 1MHz range the PLL divider needs to see.

The channel selector gives us a binary N value of 101 for ch19, so 10kHz*101=1.01MHz (this is what must come out of the loop mixer). The tripler is set by the crystal and is fixed at 33.975MHz, so to get 1.01MHz, the VCO needs to make 34.985MHz. and the phase detector will steer it until it reaches it.

The VCO output goes two ways, to the mixer to generate 1MHz as mentioned above, and to the transmit mixer where it is converted to the output frequency.

The logic table provides the N values, and multiplying them by the channel step (10kHz at the phase detector) you get the loop mixer output frequency. Add that to the tripler frequency and you get the VCO frequency. Add that to the mode selection oscillator frequency (the 7.8MHz one) and you get the final frequency.

Thats all the top row of that spreadsheet does, the rest is just filled down.

All great info but how do theybstrip off the 10kz when all is said and done? Thats possibly how my 10khz stays coupled along the path somewhere. Tomorrow I will check all the points where these freqs are and see where my 10k stays added that will be where the problem part is. Great info Brandon!Looks more complicated than it really is. The top two lines have some stuff in them but the rest is just ctrl+D to fill down. Here is a quick rundown on how all the frequencies are mixed.

View attachment 75541

The 10.24MHz goes into the PLL and is divided by 1024 to create 10kHz (this is the channel step, how much it changes incrementing N). The other side of the phase detector wants to see the same 10kHz, so it will steer the VCO up and down until it sees 10kHz.

To get that other 10kHz, the input needs to see something the divider can get down to 10kHz. The divider can only divide by so much, it has a limited divider range), so the frequency needs to be pretty low going in, around 1MHz. To get this 1MHz signal, the VCO is designed so that when it is mixed with the 11MHz tripler output (33MHz), the output is in the 1MHz range the PLL divider needs to see.

The channel selector gives us a binary N value of 101 for ch19, so 10kHz*101=1.01MHz (this is what must come out of the loop mixer). The tripler is set by the crystal and is fixed at 33.975MHz, so to get 1.01MHz, the VCO needs to make 34.985MHz. and the phase detector will steer it until it reaches it.

The VCO output goes two ways, to the mixer to generate 1MHz as mentioned above, and to the transmit mixer where it is converted to the output frequency.

The logic table provides the N values, and multiplying them by the channel step (10kHz at the phase detector) you get the loop mixer output frequency. Add that to the tripler frequency and you get the VCO frequency. Add that to the mode selection oscillator frequency (the 7.8MHz one) and you get the final frequency.

Thats all the top row of that spreadsheet does, the rest is just filled down.

dxChat

- No one is chatting at the moment.

-

-

-

@ Catalyst 122:Who do I contact for a name change. I put in for it over a year ago and it says still under review.

-